数字ic后端工具-ic后端工作累吗

《数字IC后端笔试题库》会员分享,在线阅读。 更多《数字IC后端笔试面试题库(6页珍藏版)》请在人人文库在线搜索。

1. I. 简述数字IC设计流程 2. 解释数字后端如何选择工艺节点(process node)和金属堆栈(如1P7M或1P8M)? 3、如何做好户型图? 平面图的步骤? 如何限定平面图? 4. 当设计中内存太多,不可能全部放在边界上时数字ic后端工具,是否可以将内存放在核心区? 为什么? 这样做的利弊是什么? 5 如何规划电源计划? 衡量动力计划好坏的指标有哪些? 6、影响标准细胞延迟的因素有哪些? 净延迟可以为负吗? 为什么?如果可以为负,请

2. 解释原因。 7、请说明放置步骤的作用,是做什么用的? 放置步骤中的子步骤是什么? & 在布局阶段,是否需要对时钟clock、reset等信号进行额外的特殊处理? 为什么? 9. 贴片后发现时序违例比较大,应该如何调试? 应该从哪些方面入手分析? 10、布局阶段优化时序的方法和策略有哪些? 11. 如何确定分班结果? 12. placement阶段是否需要设置clock uncertainty? 如果是这样,应该设置什么值? 13 什么是拥塞? 如果设计

3、如果n路出现严重拥堵,应该如何处理? 14 解释时钟树综合的作用? 为什么要做时钟树综合? 15. 如何判断时钟树上时钟反相器或缓冲器的类型? 是否可以使用时钟缓冲区来生长树? 16.要让工具长出一棵树,应该告诉工具什么要素? 如何限定时钟树? 17. 时钟树延迟和时钟偏斜哪个更重要? 18、时钟树太长有什么坏处? 更大的时钟偏差有哪些优点和缺点? 19.cts后clock skew有哪些部分

4、cto之后的clock skew值和cts之后的clock skew值有什么区别? 20. 对于具有复杂时钟结构的设计,给定布局约束,您能否编写时钟树约束文件(不指定时钟反相器类型、最大转换值等)? 详细说明您如何分析设计的时钟结构? 21、cts后如何分析clock tree是否合理? 22. 给定一个时序报告,需要判断路径是建立时序报告还是保持时序报告? 需要判断当前报告处于什么阶段? 分析路径是否异常(比如某个延迟值比较大等)

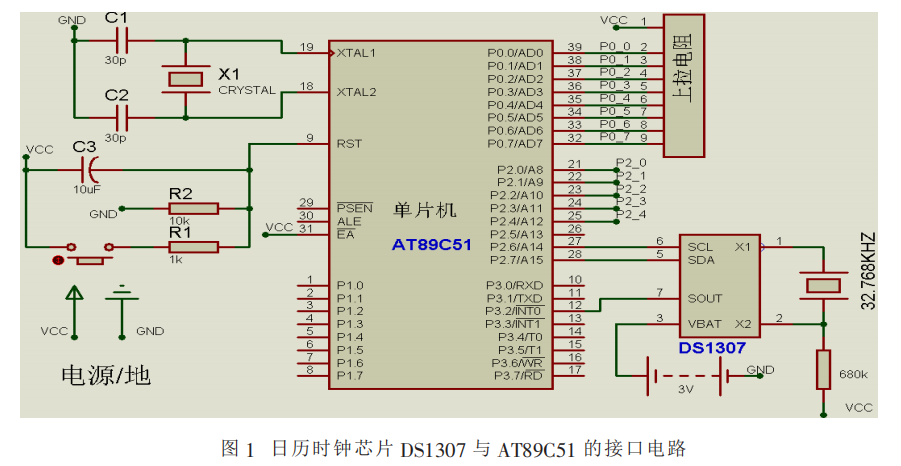

5.? 23.解释一下时钟天平的作用是什么? 分析其道理。 24.解释逻辑排他和物理排他的区别。 25、如何实现某路数据通路上的延迟值接近? 26.解释一下create_clock和create_generated_clock的区别和联系? 在cts阶段,工具在这两种约束下的行为有何不同? 27、如何计算电路的最大工作频率(时钟占空比不是1:1的情况下要特别注意)? 28. 如果您选择以下两种芯片中的一种来实现您的数字后端设计,您会选择哪一种? 请解释为什么? (1) 宽度=长度的3倍

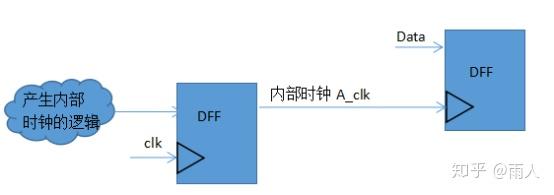

6.(2长=宽的3倍 29.解释什么是Core limited,什么是10 Limited?对于Core limited的设计,应该从哪些方面来减少芯片面积?对于10 Limited的设计,应该如何30. 如果一个芯片中有很多个10 Domain,应该注意什么问题?解释一下每个10 Domain 应该包含哪些cell? 31. 什么是SSO,设置IT时如何计算SSO 10环? 32.解释一下常见的10个cell类型是什么?它们的结构是怎样的? 33.各种模拟IP在芯片中应该如何放置?它们之间的间距应该如何预留? 34.如图,时钟和延迟

7. Latency,计算setup slack到F2输入端D,holdoF1F2CLKC1到F4输入端D。-Q) IF1/2/3/4Max0.57.00.807。 Position must be rvMin0.23.00.20.2 years 6. 35. 如果设计中有DRC(特别是spacing和short)数字ic后端工具,hold and setup violate, tape 你没有时间在out之前修复所有这些违规,所以哪一个你先修好吗哪些可以忽略? 请解释原因。 36.如果在核心

8、如果某个block上的标准单元管脚太多,可能会出现布局布线问题,如何解决? 37、使用低Vt和高Vt电池各有什么优缺点? 3&什么是PPA? 如何评估PPA? 如何实现最佳 PPA? 39、时序收敛后为什么要做静态功耗优化? 如果您在违反设置时执行此操作,会发生什么情况? 40. 如果设计中同时存在IR-drop和拥塞问题,如何解决? 41.什么是IR drop? 如果设计中同时存在IR-drop和拥塞问题,如何解决? 42 什么是 OCV? 什么是 AOCV? 它们在应用上有何不同? 43. 如何在时序签收阶段超频

9.是否考虑了V效应? 对于设置检查,降额值应该添加到发射时钟路径还是捕获时钟路径? 还是应该是发射数据路径或捕获数据路径? 等一下,这是什么情况? 44. Timing signoff阶段leakage优化的主要方法有哪些? leakage optimization、hold time fixing和max transition等DRC fixing的修复顺序应该是怎样的? 为什么? 45. Setup violation 的原因有哪些? 修复设置违规的方法有哪些?

10.什么? setup violation,芯片能流片吗? 46. 芯片即将流片。 我发现既有setup violation,也有hold violation。 应首先修复哪部分时序违规? 为什么? 如果最大转换违规发生在保持角,你需要修复它吗? 为什么? 47.GBA和PBA指的是什么? 这两个存在的意义是什么? 48 什么是串扰? 串扰如何影响时序? 如何防止串扰? 如何消除串扰? 49 什么是天线效应(Antenna Effe

11.克拉)? 天线效应的主要原因是什么? 如何消除天线效应? 50 什么是闭锁? 在芯片设计和实现阶段如何考虑和避免闩锁? 51、芯片中加入tapcell有什么作用? 为什么有的芯片不加tapcell? 解释端盖细胞的功能? 52 什么是逆温效应? 53 什么是生态? 数字IC后端实现Function ECO需要考虑哪些因素? 解释一下Function ECO的流程? 54 什么是扫描链重排序? 为什么需要扫描链重排序? 使用该功能有哪些注意事项? 55 什么是隔离室? 什么是电平转换器单元? 电平转换器的主要类型有哪些? 这两类细胞什么时候需要加入呢? 添加这些类型的单元格时,它们应该放在源区域还是目标区域?

上一篇

上一篇