数字ic后端工具-数字ic后端待遇

什么是数字后端设计?

Digital back-end数字ic后端工具,顾名思义,就是数字IC设计流程的后端,是数字IC设计岗位的一种。 在IC设计中,数字后端的人数一直是最多的,而且随着芯片规模的不断扩大,后端工程师的人数也会增加。

一般来说,数字后端可以分为工作类别:逻辑综合、布局布线物理设计、静态时序分析(STA)、功耗分析、物理验证等工作。 对人才的需求进一步增加,这也是现阶段数字后端工程师招聘量巨大的原因。

数字后端设计和数字前端设计有什么区别?

数字芯片设计流程

与数字前端设计(数字IC设计=数字前端设计?)相比,后端设计分为5个步骤。 要做的事多,所以招的人也多。 在一些大公司,5每一步都有专人负责。 后端设计工程师需要掌握的东西很多,但并不要求每一项都精通,是一个很好的选择~

后端和前端一样,也是很早就出现的一个非常重要的岗位。 虽然由于工作性质的原因,其对代码编写的要求相对于前端来说要低一些,但是各种EDA工具的使用,多种脚本语言的掌握,分析报告,纠错等都是其核心技能。 如果你对编程不感兴趣,想从事数字IC设计工作,那么选择数字后端是非常合适的。

因此,对比数字后端和前端,不存在谁好谁坏的问题。 两个职位的薪资和发展空间大致相当。 求职的时候建议大家多根据自己的技能基础和个人意愿来选择~

数字后端设计工程师做什么的?

① 逻辑综合(Synthesis)

主要负责将RTL代码转换成实际后端使用的网表网表,一个好的网表对布局布线工作起着决定性的作用。 有必要尽可能地优化性能、功率和面积。 特别是在当今要求高性能的设计中,对综合的要求非常高。

合成的质量在很大程度上取决于合成软件的性能。 业界流行的两种综合工具是 Synopsys 的 Design Compiler 和 Cadence 的 Genus。 熟练使用这两种工具是综合工作的基本条件。

② 布局布线(PD)

布局和布线是数字后端工作的最大部分。 主要负责网表到GDSII的转换过程。 步骤包括Floorplan、Place、CTS、Optimize、Route、ECO等,确保其负责的模块满足时序和物理制造要求。 . 同时,需要配合其他工程师及时提供他们需要的文件,如def、spef、netlist等,是数字后端中的核心工作。

布局布线对工具的依赖性强,工具操作相对复杂。 Cadence的Innovus软件和Synopsys的ICC在业界比较常用。 掌握这两个工具的使用需要一定的时间。

③ 静态时序分析(STA)

静态时序分析简称STA。 时序验证分析是数字后端的重要组成部分。 芯片需要满足各种拐角下的setup和hold时序要求以及其他transition、capacitance、noise等要求。 STA需要制定整个芯片的sdc约束文件,需要signoff的corner和整个芯片的时序生态过程来选择芯片。 这是一项要求很高的工作。

静态时序分析通常需要掌握Synopsys的primetime和cadence的tempus的使用方法。

④物理验证(PV)

物理验证也是流片前的重要项目。 如果物理验证错误,则芯片生产将失败。 在布局布线工具中,软件只能检查金属层上的物理违规,而真正的物理验证需要检查器件的底层(base layer)。 因此,物理验证需要将金属层和底层金属结合在一起,对芯片进行全面的drc检查。 同时,还需要做全芯片LVS(版图与原理图一致性检查)、ERC(电气规则检查)。 确保芯片没有任何违反物理设计规则的行为。

实物验证一般在导师公司口径上进行,是行业标准的实物验证工具。

⑤ 功率分析(PA)

功耗分析也是芯片验收的重要部分。 随着芯片规模越来越大,功耗在芯片中的地位越来越高。 电源分析的两大任务是分析IR drop(电压降)和EM(electromigration)。 将结果及时反馈给布局布线任务组,以便他们及时修改后端设计图,解决设计中的潜在问题。

一般功耗分析使用的工具有Ansys公司的redhawk、cadence公司的voltus和synopsys公司的ptpx。

而且,数字后端工程师通常以一个项目组为一个团队,上面提到的任务会被分成不同的角色。 通常,一个项目中会有一名顶层工程师、一名STA工程师、一名功率分析工程师、一名物理验证工程师和数名模组工程师。 这些工程师需要互相配合,才能完成整个芯片从RTL到GDSII的过程。 ,同时确保没有时序和物理验证违规。

数字后端设计工程师所需的技能

数字后端主要以软件工具为主,需要掌握以下软件(主要是cadence、synopsys、mentor公司)

地点和路线: Innovus/Encounter,ICC2/ICC

合成:DC,属

物理验证:口径

静态时序分析:PrimeTime、Tempus

电源分析:Redhawk、Voltus、PTPX

每个平台都需要您掌握不同的技能。 通常,您只需要为每个平台学习一种工具。 一个初级工程师也很难掌握所有这些技能。 如果您知道如何使用这些工具,您将成为一名老司机。

由于数字后端工程师需要运行一些自动化的任务,因此也需要掌握必要的脚本语言。 比如掌握以下知识就比较重要:

verilog

TCL公司

Perl

Python

所有的技术岗位主要看两点:专业技能(skills)和项目经验(experience)。 所以除了上面列举的这些技能之外,能真正做到一两个项目也是很重要的,哪怕是一些小模块的后端设计,尤其是项目过程中积累的调试经验。

数字后端设计工程师的薪资和职业发展

免责声明:数据来源于网络,如有错误,请联系更正

这是2021年后端设计秋招的最新薪资情况。 一线城市平均工资在25万左右,二三线城市略低。

另一个好消息是国家现在大力发展集成电路,所以这几年工资一直在上涨,而且这个趋势应该会在五年内持续下去。

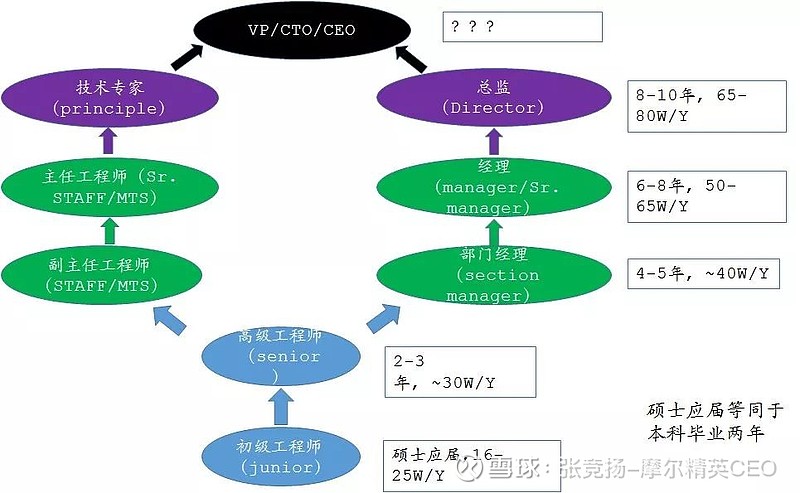

数字IC设计工程师(前后端)职业发展路径

关于数字后端设计工程师的职业发展,未来IC设计工程师的职业发展分为两条路径:一是技术专家路线,基本遵循上图的发展阶梯。 这些人永远是技术型的,成为高级设计工程师; 二是项目管理路线,有些人会成为设计经理,做一些管理工作。

做设计工程师多年后,少数人也可以跳槽,比如转做架构工程师,在EDA公司做应用工程师(AE),或者干脆创业。 但总的来说,绝大多数设计工程师还是会继续工作的,毕竟这个职位还是一个天花板很高的职位。

数字后端设计工程师入职门槛及条件

现阶段数字后端工程师主要招研究生和本科生,但好在对专业的要求不是很严格,集成电路方向不是必须的。 只要掌握了以上技能,即使是无关专业,如材料、物理、自动化、机械等理工科专业,也可以成功申请数字后端设计工程师。

如果您拥有学士学位,请不要气馁。 有工作经验的本科生仍然可以找到数字后端工程师的职位。 普通学校毕业的学生不要气馁。 985高校的毕业生在求职的时候肯定是有优势的,但是毕竟每年的毕业生都不多。 在IC产业整体供不应求的背景下,企业仍会从排名一般的学校招收学生。 学生,当然前提还是一样,要有专业技能(skills)和项目经验(experience)。

找工作,选择比能力更重要。 如果一开始就选对了行业和岗位,成功会比较容易。 当今的IC设计行业,有“钱”就有未来。 不用说,薪水很高。 如果进入合适的公司,拿到股权,就可以轻松实现财务自由。 可以说是理工科学生的黄金工作之一。

如果你之前没有学过Verilog,没有做过集成电路相关的项目,没有任何基础,那么推荐你来电子课网的《数字后端设计工程师就业班》( E-course.net网站链接专注于集成电路设计教育培训6年),不少同学通过E课网的学习掌握了以上技能,也积累了一定的项目经验。 和别人竞争的时候,有项目经验的肯定比只学过基础理论的有优势。

所以Ecourse.com就业课堂为大家解决的重点问题是:就业! 拿高薪! 每个学生完成课程后,都能具备专业知识和能力,进入高薪名企,就业后完全胜任工作职能。

零基础的理工科生不要错过。 更多易科网IC设计就业班详细信息,可以点这里→→,现在是入行的最佳时机数字ic后端工具,以后门槛只会越来越高,早报名早进入~

E-course.net(网页链接)是专业的集成电路教育平台,六年来致力于半导体行业高素质集成电路专业人才的培养。 该平台以集成电路企业岗位需求为导向,提供契合企业环境的培训平台。 通过线上线下相结合的培训方式,快速培养出满足企业需求的学员。

E-course.com拥有成熟的培训平台、完整的课程体系、强大的师资力量。 在国内规划了168门优质半导体课程,覆盖集成电路全产业链,拥有4个线下实训基地。 截至目前,累计深度培训15367人次,直接向行业输送专业人才4476人次。 与143所高校建立深度合作关系,为企业举办集成电路专题培训班240期。

今天是《半导体行业观察报》分享的第2598期内容,欢迎关注。

上一篇

上一篇