内存频率 前端总线-cpu前端总线(fsb)频率

2017年底,就在很多人放下工作,准备过元旦假期的时候,中国处理器带来了一个重磅消息——12月28日,上海兆芯集成电路有限公司正式发布了本期杂志报道此前多次基于五道口处理器架构,代号ZX-D,官方型号为兆芯开先KX-5000系列国产新一代x86处理器。

我们知道目前各种家用PC和服务器中的处理器都是基于x86架构的,无论是Intel还是AMD的产品,那么我国研发的这款x86处理器到底有什么样的实力呢? 当用户已经有大量国外产品可供选择时,自己打造x86处理器还有意义吗?

打造国产x86处理器的必要性

据说习惯成为自然。 相信当你用电脑浏览这篇文章的时候,用电脑玩《绝地求生》或者写各种办公文档和代码时,都不会觉得有什么问题。 然而,在中国计算机研究人员的眼中,可能有一种无奈,因为这些x86计算机中的处理器几乎都是国外产品。

这绝不是一种狭隘的爱国主义,而是对行业缺乏的一种遗憾。 当DIY玩家在比拼你的英特尔处理器好还是我的AMD处理器好时,他们可能没有想过我国一年进口多少处理器。 国家核高专专项总工程师、清华大学微电子研究所所长魏少军在发布会上谈到了这个问题。

▲中国科学院院士、中国科学院上海高级研究院院长王曦院士(第一排左三); 中国科学院院士、上海市集成电路行业协会名誉会长、上海华虹鸿利半导体制造有限公司科学顾问邹世昌院士(第一排左四); 国家核高专专项总工程师、清华大学微电子研究所所长魏少军先生(第一排左二); 中国科学院国家核高专专项技术、通用芯片与基础软件研究副总工程师 中心主任李明舒博士(第二排左三); 工信部电子信息司集成电路处处长任爱光(前排右二)等多位领导出席兆芯开先KX-5000处理器发布会。

虽然说我国的集成电路在过去几年取得了长足的进步,但我们也应该非常警惕自己存在的问题。 魏少军主任提到了一个典型的例子,中国每年仍然要花费巨额资金进口集成电路。 2017年集成电路年进口额达2500亿美元。 如果仔细分析import结构,会发现CPU占了很重要的一部分。 . 在这2000多亿美元中,与CPU相关的进口额约为550亿至600亿美元。 显然,这个数值不仅是我国集成电路产业的巨大损失,也意味着集成电路产业的发展并不完善,在处理器领域长期受制于人。

另一方面,对于中国这个世界上人口最多、政治、经济、科技、国防等方面发展突出的大国来说,信息技术产品长期依赖进口也是安全隐患。 为此,我国在2006年设立了核高基项目。核高基是核心电子器件、高端通用芯片和基础软件产品的简称。 并行的16个重大科技项目之一。

魏少军主任说,核高技术专项是国家中长期科技发展规划的第一个专项,也叫01专项。 01专项解决的问题,简而言之就是三类产品。 首先是CPU; 二是操作系统; 第三是组件。 CPU无疑是核高技术项目中的重中之重。 也可以说,整个国家的信息安全上面是连起来的,我们的产业安全下面是连起来的。 所以如果不能突破CPU和操作系统,就意味着核高专项的成果将大打折扣。

因此,在开展核心高基CPU项目的同时,中国计算机科研人员也在努力打造两件事——围绕CPU构建完整的产业链,从设计、制造、封装、测试到整机应用。 毕竟,没有良好的产业环境和完整的产业链,很难制造出一款成功的处理器; 同时,中国科研人员也在不断尝试探索如何组织和执行CPU、操作系统等高难度任务内存频率 前端总线,并初步找到了一种软硬件结合、驱动整机、环环相扣的模式。产业链。 “要真正解决问题,找到适合中国特色的发展道路,”魏少军主任说,但这条道路对中国科技人员来说确实是一条艰难的道路。

国产x86处理器的难点

“虽然参加了CPU发布会,但今天主要想聊聊研发难点和投资分析。” 国家核高专专项副总工程师、中科院通用芯片与基础软件研究中心主任李明舒博士一站上讲台就发表了讲话,这样的感慨也表露无遗兆芯投资的诸多细节——兆芯牵头的核高技术项目是核高技术项目史上最大的资助项目。 总金额57亿元,其中核高技术基地投资15.6亿元,上海市政府支持15.6亿元,其余为企业自筹。 也就是说,整个兆芯项目,包括CPU、操作系统、整机、技术,总投资57亿元,其中有不少是兆芯自己的积蓄。 上调。

▲国外处理器的研发投入远高于国内处理器。

57亿元的数额虽然看似很多,但与其他处理器厂商的投入相比,并没有优势。 首先,由于x86处理器在我国起步较晚,很多技术和协议的使用需要资金获得国际授权,其次是司空见惯,研发和制程成本高昂。 根据李明舒博士通过公开报道收集到的信息,IBM Power 8处理器的研发成本约为24亿美元; AMD Zen架构研发耗时约5年,耗资55.82亿美元,计算架构投资约31.26亿美元。 数值上可能有出入,但估计也要花费数十亿美元的研发费用。 英特尔现在每年花几百亿在研发上,我们却花几十亿RMB去做别人花几十亿甚至几百亿做的事情。 这真的很不容易。

那么在投资有限的环境下,新一代国产x86处理器取得了哪些成绩呢?

兆芯开先KX-5000系列处理器架构取得重大进展

首先,中国科学院院士、中国科学院上海高等研究院院长王曦院士认为兆芯开先KX-5000系列的发布是中国处理器非常重要的突破. 任爱光主任表示,这个项目是所有主任教师中投入最多的项目。 今天兆芯开先KX-5000系列的发布,是我们迈出的第一步。 当然,更令人兴奋的是,接下来,上海兆芯集成电路有限公司董事长叶军先生和上海兆芯集成电路有限公司总工程师王伟林先生将进行技术交流。兆芯开先KX-5000系列处理器评测。 详细介绍。

▲先生上海兆芯集成电路有限公司董事长叶军在会场正式发布了兆芯开先KX-5000系列处理器。

开先KX-5000系列处理器是兆芯国内首款采用SOC设计、基于五道口架构的自主可控通用CPU。 它采用 28nm 技术制造,具有 4 到 8 个内核。 同时也是国内首款支持双通道DDR4内存的CPU。 其187平方毫米的芯片内共有21亿个晶体管,最多可集成8个CPU核心和显示核心。 处理器显示核心支持高清4K解码。

▲现场展示了采用兆芯开先KX-5000系列4核和8核处理器的整机,可以流畅播放4K视频。

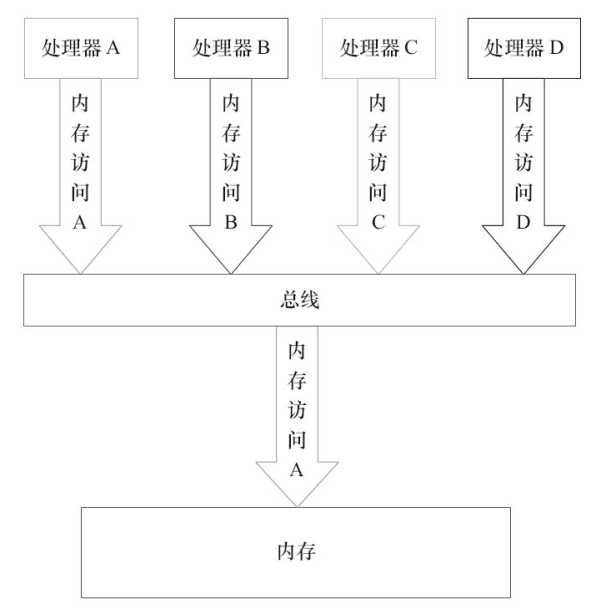

SOC设计的意义何在? 在之前的兆芯ZX-C+8核处理器上,其结构是由两颗ZX-C四核处理器封装在一起的。 从外观上我们可以看到PCB基板上有两个小磁芯。 问题也随之而来。 多核处理器在工作时,需要保证每个核能“看到”的缓存内容是一致的,知道哪些数据被改写了,哪些任务应该由哪个核执行,从而避免冲突和效率最大化。 因此,需要时刻保持同步,以保持缓存的一致性。

但ZX-C+处理器只是一个纯粹的计算核心。 为了使每个四核模块中的缓存保持一致,需要将协调工作交给外部北桥芯片——需要同时更新两个四核模块。 当缓存在设备中的数据存储时,会通过FSB前端总线传输到北桥进行更新。 虽然缓存的数据量不大,但由于需要通过北桥进行处理,无疑会有一定的延迟,核心之间的通信也会变慢,从而对处理器的性能造成一定的影响程度。

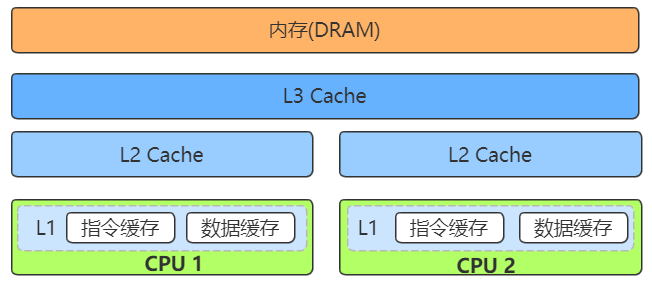

▲开先KX-5000系列处理器采用的五道口架构示意图,类似于AMD ZEN架构,每4个核心组成一个集群,即一个模块,模块之间通过点对点的方式互连点直网。 内核共享 4MB L2 缓存。

在开先KX-5000系列处理器中,不仅增加了缓存容量,四核各共享4MB缓存,一共8MB缓存。 更重要的是,处理器与北桥的完全融合,使得缓存数据的一致性直接在处理器内部完成。 这意味着处理器之间的交互不再需要通过北桥,而是采用片内高速点对点直接网络互连,降低了延迟,提高了带宽。 它的架构很像AMD的ZEN,可以说是英雄。 观点差不多。

其次,内存控制器和PCIe控制器的整合,也可以大幅提升内存和显卡的性能。 在南北桥架构中,内存和显卡必须通过北桥通过FSB前端总线向处理器传输数据。 但问题是,在ZX-C平台中,FSB前端总线频率仅为1333MHz,理论最大带宽约为10.6GB/s。 在开先KX-5000系列处理器中,处理器内部集成了DDR4内存控制器和PCIe控制器,处理器可以通过内部高带宽直连总线访问内存和显卡。 兆芯数据显示,内存访问带宽提升至单核12GB/s,多核17GB/s。 内存带宽的增加,可以更好的发挥处理器的计算性能。

更重要的是,兆芯开先KX-5000系列采用的五道口架构通过减少新的核心流水线设计、改进的分支预测、改进的乱序执行算法、翻倍的带宽、新的内存访问单元,减少了五级流水线处理器单核性能提升25%,多核性能提升1.4倍。 同时兆芯还为KX-5000系列设计了型号为ZX-200的IO扩展芯片(即提供扩展能力和功能模块的主板芯片组,类似Intel Z370和AMD X370),可提供9个PCIe 2.0频道。 共有 11 个 USB 端口,包括两个原生 USB3.1 GEN 2 端口。 重要的是要知道英特尔的 Z370 主板仍然不能原生支持 USB 3.1 GEN2。

▲采用8核8线程设计,主频2.0GHz,搭载兆芯开先KX-U5680处理器,8MB缓存。

▲ 采用4核4线程设计,主频2.0GHz,搭载兆芯开先KX-5640处理器,4MB缓存。

同时,在产品布局上,与英特尔的酷睿i3、酷睿i5类似,兆芯此次在开先KX-5000系列上布局了多款产品,定位较低的有KX-5540、KA-5640等。 从1.8GHz到2.0GHz,采用四核四线程设计; 定位较高的产品数字型号前有英文U,如KX-U5680、KX-U5580M、KX-U5580M,均采用8核8线程设计。 它们的区别主要在于工作频率的设置。 此外,兆芯还面向服务器和存储领域推出了基于五道口架构的KH-20000系列。 相比普通的开先KX-5000系列,最高支持128GB内存,支持RDIMM/ECC内存。

▲ 开先KX-5000系列家族一览

▲兆芯开先KX-5000系列8核处理器达到了主流处理器的性能标准

至于大家最关心的性能表现,兆芯这次也放出了多项数据。 兆芯开先KX-5000系列8核处理器在SPEC2006中的整数单任务性能为19.9,多任务得分为115。在DIY玩家常用的FrizChess棋类计算测试中,其性能达到了791.1万步/其次,7-zip综合得分为12122MIPS,CINEBENCH R11.5 CPU渲染得分为4.01pts。

从这些测试结果来看,兆芯开先KX-5000系列8核处理器的性能基本达到了第六代酷睿处理器Core i3-6100的水平。 酷睿i3-6100处理器在FrizChess国际象棋计算测试中跑分758.8万步/秒,CINEBENCH R11.5 CPU渲染得分4.35pts,7-zip综合得分11236左右。来自ZX-C处理器依然在使用南北桥架构和FSB总线在性能上赶超第六代酷睿i3处理器,这对于兆芯国产x86处理器来说确实是一个非常大的进步。 将兆芯开先KX-5000系列的发布称为“中国处理器非常重要的突破”,王曦院士显然不为过。

瞄准个人用户市场

未来更值得期待

会后,本刊还对上海兆芯集成电路有限公司董事长叶军先生、上海兆芯集成电路有限公司总工程师王伟林先生以及上海兆芯集成电路有限公司进行了专访。还采访了国内x86处理器的两位负责人。 揭示了更多关于国产x86处理器的应用、市场需求,以及未来兆芯处理器的发展方向。

▲会后,上海兆芯集成电路有限公司董事长叶军先生(图左)与上海兆芯集成电路有限公司总工程师王伟林先生(图右)图),接受了本刊专访。

首先,叶军先生介绍,除了在一些国家单位得到应用,值得一提的是,基于兆芯处理器的联想电脑也在十九大上得到了应用,全程保障。中国共产党第十九次全国代表大会。 根据会场反馈,国产整机在会议期间运行稳定,性能好,适用性强,得到一致认可。 同时,兆芯处理器的安全性,对SM3、SM4高速国密算法指令的支持,以及对各类政务、机密文件的快速加解密能力,也是国外其他处理器所不具备的,这也说明兆芯已经能够很好地满足政府部门、军队、金融等专业市场的需求。

不过,这个市场的体量并不大。 全国库存只有200万台左右,每年的总采购量也只有几十万台。 同时,还有来自其他国产处理器的竞争,因此市场份额仅占整个CPU市场的5%。 因此,兆芯要想获得更好的发展,就必须争取剩下的95%的个人用户市场。 这个市场虽然国内没有竞争,但有英特尔和AMD两大巨头。 兆芯非常希望在市场上与他们竞争,但发展进步必须一步一个脚印。

▲兆芯处理器发展路线图,KX-6000将改用16nm工艺,KX-7000将采用全新架构。

为什么不将现在的兆芯处理器一步到位,升级到与Intel、AMD产品相当的频率,并配备更多的缓存呢? 王伟林先生解释说,我国处理器与竞争对手的主要差距还是在技术上。 仅仅有好的想法和设计是不够的。 处理器的架构设计必须根据自身的技术水平来确定。 如果技术跟不上,还是不行。 完成。 当然,兆芯也在努力追赶更先进的生产技术。 比如在研的KX-6000将采用16纳米工艺,单核频率3.0GHz,可支持DDR4 2800和3200内存。

KX-6000将探索高频下的设计过程,包括从pcb/substrate/power plan研究PI/SI问题,以及高频时序收敛问题。 同时,新的处理器微架构也在筹备中,兆芯的新互联架构KX-7000将进一步升级,核心已经有了一定的发展。 据兆芯测评,其单核性能较同频KX-5000提升1.4~1.5倍,并支持PCIe 4.0、DDR5等未来前沿技术标准。

“从近2~3年的目标来看,兆芯的目标是具备自主造血能力,逐步提升处理器销量,尽快实现年销量百万,那么兆芯不仅要实现支付,还能有效扩充我们的研发团队,加大研发投入,赋能兆芯处理器的持续发展。” 采访的最后,叶军先生提出了自己的期待。 显然,兆芯处理器绝不是一个依赖外资的形象工程,而是一个旨在攻克技术难关、融入市场化经营的务实工程内存频率 前端总线,对我国处理器产业的发展具有重要意义。 我们期待95%的x86处理器市场迎来三大支柱的那一天。

上一篇

上一篇