数字ic后端工程师-数字ic后端

IC设计工程师是从事集成电路开发设计的职业。 随着我国IC设计行业越来越好,越来越多的工程师加入到这个新兴行业。 成为IC设计工程师的门槛比较高。 往往需要有良好的数字电路系统和嵌入式系统设计经验,了解ARM体系结构,有良好的数字信号处理、音视频处理、图像处理和一定的VLSI基础。

因此,不少在校学生希望了解IC相关工程师在企业的具体工作内容、技能要求、发展前景等,以增加就业竞争力。 增加相关方面的知识储备,提前熟悉工作内容,提前做好职业规划。

为此,本文在拿到offer后,为大家详细揭秘集成电路设计岗位数字IC后端攻城狮的工作内容和工作强度,为大家提供职场经验和前辈的建议,希望对各位同学有所帮助。

01

数字IC后端攻城狮

数字IC后端工程师是芯片微观世界的架构师,负责将前端工程师的设计图转化为实际的电路结构,生成符合厂商要求的GDS文件。

02

工作内容

包括但不限于:数字物理设计、综合网表编辑、路径地址解析协议流程的实现、在合理时序约束下完成时序收敛、完成厂商设计规则检查等物理设计要求。 一般来说,数字IC后端工程师会经常和模拟IC前端设计师、厂商技术人员、封测技术人员交流。 广义上来说,又细分为以下几个方面:

01

放置

主要涉及STD细胞的访问。 这一步基本上是EDA工具根据模块的分布优化的。 但是数字ic后端工程师,如果时间有问题,仍然需要一些人为干预。

02

华侨城

即时钟树(简称CTS)是驱动电路中的一个时序单元。 一般使用平衡树(简称BTS)。 但是,随着涉及的频率越来越高,现在一些逻辑较深的路径往往会用到有用的skew技术。

03

路线

即绕线,一般在满足厂商设计规则检查的情况下,通过EDA工具完成自动布局布线。 随着技术的发展和成熟,EDA工具可以优化关键时序路径的层级提升,利用延迟较小的高层金属来优化时序。

04

RC/STA/DRC/LVS/正式

为了获得真正可以交付生产的文件,需要在给定的时序约束下迭代优化时序,并执行设计规则检查、布局网表一致性检查和优化网表功能一致性检查等多项任务。

03

技术储备

01

基础理论知识包括CMOS相关知识、半导体基本原理、数字电路设计知识等。

02

必要的工具包括EDA工具中的workshop和UserGuide以及shell或python等脚本语言。

03

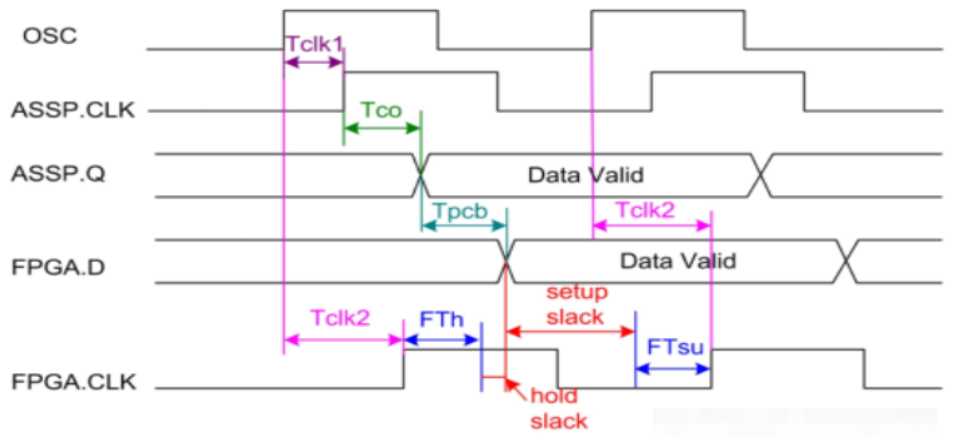

另外,为了打造自己更上一层楼的技术壁垒,还需要深入研究STA的原理; 了解不确定性/设置/保持时间的时序相关知识; 了解一些模拟射频IP如PLL、SENSOR等的特殊要求; 熟悉高速IO设计、包房、封装测试需求; 清楚ARM核、PCIE、DDR等一些常用IP的典型功能设计程序或数据流。

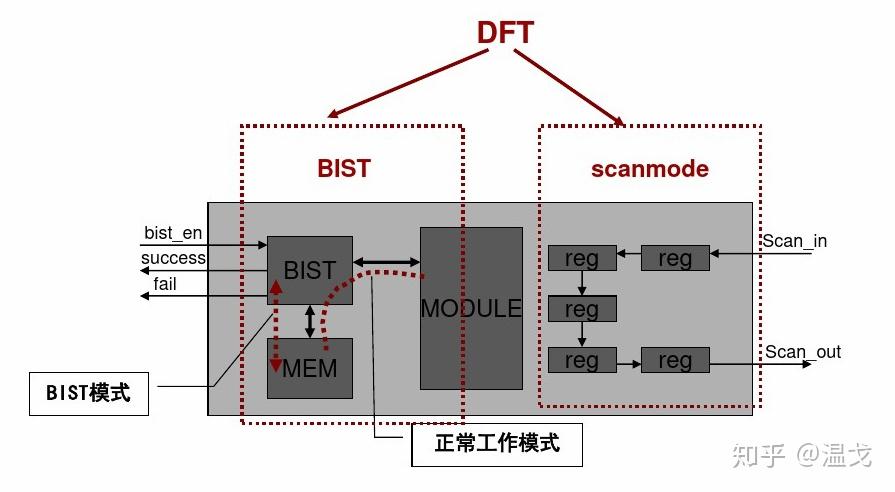

04

为了区别于普通后端工程师,最好深入学习power planning; 知道如何在不同的测试模式下实现测试能力/覆盖率; 了解如何筛选芯片以降低封装测试成本; 熟悉如何从时序、功耗或其他层面提高芯片良品率。

04

工作强度

主要看项目时间周期。 基于数位IC后端的特性,通常流片前夕是工作强度最高的时期,因为数位IC后端工程师的工作进度会严重影响版图及产品能否上线按时提交。

虽然大公司的流程比较完善,整体负载也比较均衡,但项目中的任何一个细节都会影响到整个流片,所以数字IC后端往往逃不过任何一个环节出错造成的进度延误。

05

前景

数字 IC 后端是一个高需求和高增长的行业。 随着芯片产业的蓬勃发展,生产规模越来越大,芯片集成的复杂度越来越高,社会对数字IC后端设计人员的需求势必越来越大。 所以工作机会多,跳槽也很容易。

一般来说,后端设计上手容易,提升难。 因为后端设计涉及到的工序较多,所以比前端设计更通用。 但是,要想独立数字ic后端工程师,就需要不断的积累。 走技术专家发展道路。 但是,如果你涉及设计、IP、封装、测试、技术等,你也可以转型成为PMO或者自己创业。

06

资深建议

打好基础,注重积累理论知识,注重实践,积极主动,多请教,多学习。

上一篇

上一篇