魏少军 人工智能芯片-魏少军 我们的芯片买

近两年,人工智能(AI)很热,预计未来还会再热一段时间。因此,在今天上午ASPENCORE旗下《电子工程专辑》、《电子技术设计》、《国际电子商情》三大媒体联合举办的“2019年中国IC领袖峰会”上,中国半导体行业协会副理事长、设计分会理事长魏少军教授以“人工智能芯片要上一个新台阶”为题,探讨了他最近关于AI的一些思考,以及关于AI芯片发展的大概愿景。th5ednc

AI芯片的四个阶段

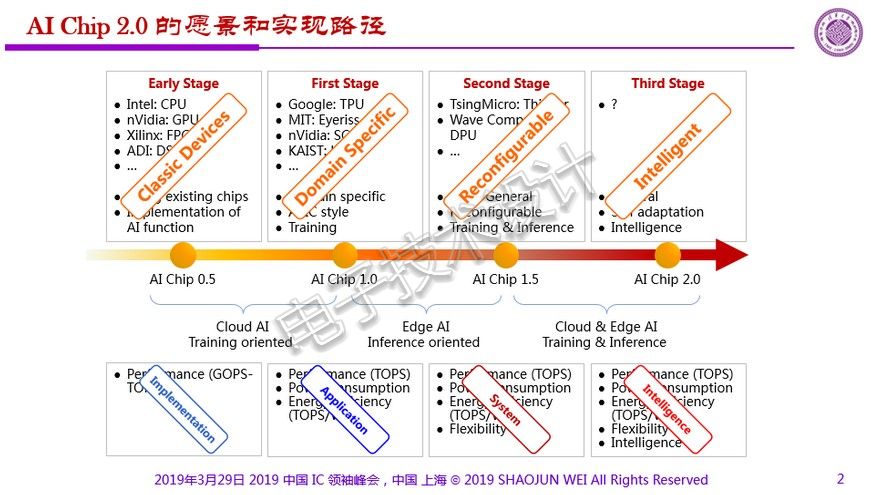

首先,魏教授将AI芯片的发展划分成四个阶段:AI Chip 0.5、1.0、1.5、2.0。th5ednc

th5ednc

AI Chip 0.5阶段是指利用已有的芯片(如CPU、GPU、FPGA、DSP等)来实现AI功能。这是比较早期的实现方式,只要实现AI功能就好。th5ednc

AI Chip 1.0阶段出现了一些AI专用芯片,比如TPU、SCNN、UNPU等。它们属于领域专用,根本点在于如何解决强大的算力和功耗之间的关系,也即寻求一种最佳的效率(OPS/W)。魏教授指出:“各种人工智能的算法都需要强大的算力,而用原来的芯片去做无可避免地会带来功耗的上升。因此,我们需要开发一些专用芯片,在保持算力的同时降低功耗。”th5ednc

AI Chip 1.5阶段出现了一些半通用、可重购、兼顾了训练和推理的芯片,比如Thinker、DPU等,用来解决算法太多等问题。目前这类芯片所报道的还不是特别多,我们还主要处在AI Chip 1.0阶段。th5ednc

AI Chip 2.0阶段是什么?我们现在不知道。魏教授认为它应该是通用的,同时应该是自适应。“当然,我们希望它是智慧化的。”他补充说。th5ednc

早期的AI Chip 0.5-1.0主要聚焦在云端的训练。1.0-1.5开始较多地讨论边缘端、与推理相关的内容。“但这并不完全集中在推理,未来的发展应该是两者兼顾。”魏教授说。因此,从1.5-2.0应该是云和端、训练和推理兼顾的一项发展。th5ednc

每个阶段大家聚焦的重点是什么呢?0.5阶段主要聚焦于性能,即怎么样能够运算得更快一些。这中间经历了从CPU(速度不够快)到GPU(功耗很大)再到FPGA实现的转变。1.0阶段不仅仅关注性能的问题,更关注能耗(能量效率)的问题。1.5阶段除了性能、功耗和能效外,更关注的是灵活性。2.0阶段则包括更重要的智慧化。一言以蔽之魏少军 人工智能芯片,0.5阶段是实现,1.0阶段是应用,1.5阶段是系统,2.0阶段是智慧。th5ednc

综上,2.0阶段与上述发展特征相吻合,而前面则不吻合。魏教授认为,这个收敛过程恰好也说明了任何事物发展都有它自身的特点,殊途同归最终都要做到智慧化。th5ednc

AI Chip发展路线图

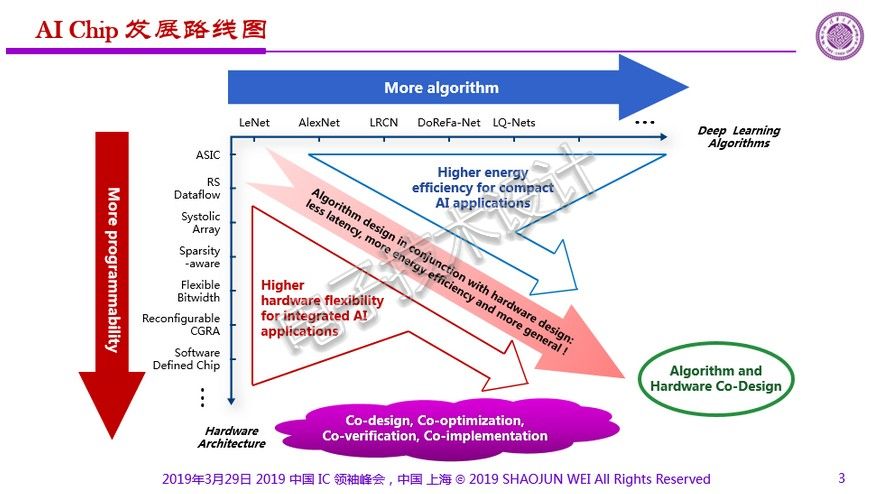

AI芯片到底会怎么样发展?从下面的AI Chip发展路线图来看,这类芯片会慢慢出现两种不同的架构:越来越多的算法;越来越多的可编程性。同时,算法的设计和硬件的设计两者要结合起来,目标是实现更低的延时、更高的能量效率魏少军 人工智能芯片,以及更通用。因此,在这个过程当中,算法和硬件的联合设计,成为AI芯片发展的重要特点。th5ednc

th5ednc

此外,图中右上角所述的“更高的能量效率面向小型化的AI应用”,主要是指边缘应用。而左下角“更高的硬件灵活性面向综合的AI应用”,则更多地聚焦云端应用。“这样的发展路线图,基本上可以反映在发展过程当中所面临的不同问题,和要解决的重点问题。”魏教授认为,我们在设计AI芯片的时候,已不像以前只关心芯片或关心软件,而是需要协同的设计、协同的优化、协同的验证和协同的实现。th5ednc

AI服务需要从“云”走向“端”

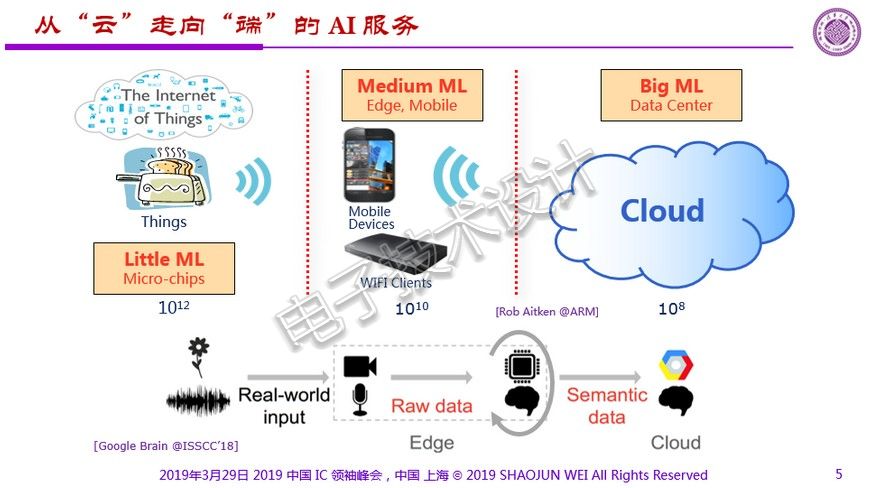

今天的AI服务更多还是在云上,阿里巴巴、Google、百度、IBM、Microsoft等都在发展AI云服务。这类服务内容已经很丰富,包括图像识别、语音翻译、智慧家庭、智慧医疗等等。th5ednc

但芯片人更多的是希望从云走向端,有足够的量才能实现我们的愿望和现实利益。以下面Arm公司的例子来看,它把AI应用分成三类:大端(云端)、中端和小端。从数量上看,大芯片、中芯片、小芯片各有100倍的差距。但是不管怎么做,云端和边缘端的协作是必然。th5ednc

th5ednc

ASIC增速将最快,但有两个问题难解决

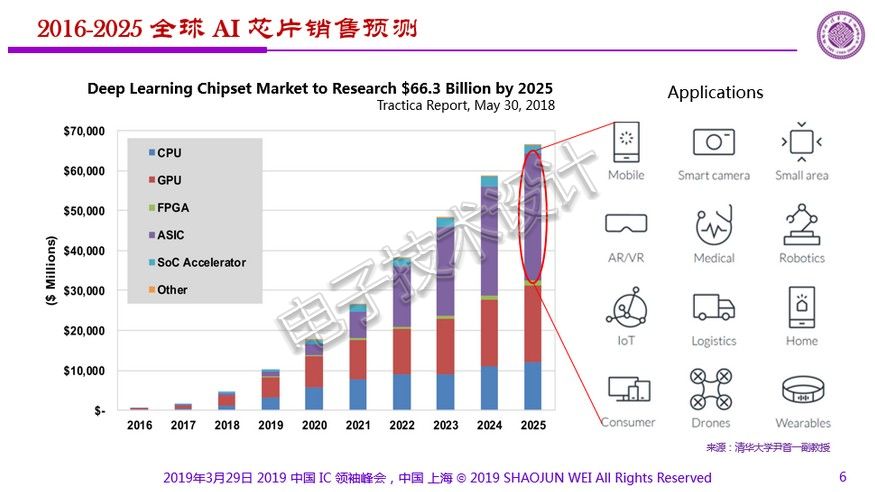

从Tractica的报告来看,各类AI芯片中,专用集成电路(ASIC)的数量增长将最快。这个预测基于的点是什么?就是大量的应用在端,需要用到更多的领域专用类芯片。th5ednc

th5ednc

但这其中我们碰到两个问题:第一个是算法仍在不断演进,新算法层出不穷;第二个是一种算法对应一种应用,没有统一的算法。这对于做ASIC是件非常痛苦的事情,这在短期也很难解决。th5ednc

举例来说,卷积型的CNN更多的是用于视觉特征的提取;全互联的FCN更多的是用于分类;RNN则主要用在串行数据的处理上,比如说语音的识别和翻译等等。th5ednc

th5ednc

因此,我们很难有一个具体的算法,能够覆盖各种各样的应用——实际上,神经网络的结构是不太一样的。th5ednc

此外,在不同的应用当中,能量指标也不太一样。比如,可穿戴设备、智能传感器等的功耗大概是1mW;移动电话、智慧家庭、智慧玩具等是100mW;视频监控、工农业应用可能会达到瓦级;而到了自动驾驶则可能会上百瓦。th5ednc

能量效率指标在不同应用中要求不同,要想全部覆盖也是个比较麻烦的事情。th5ednc

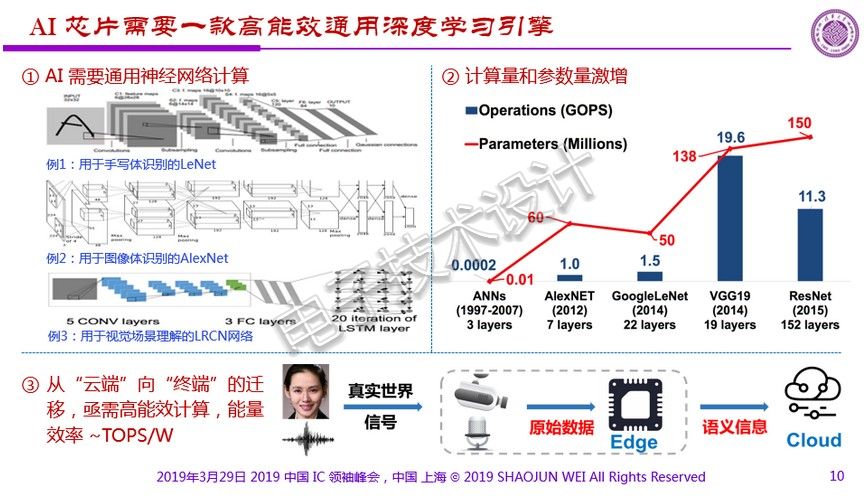

AI 芯片需要一款高能效通用深度学习引擎

总的来说,我们需要解决下图中的三个问题。比如说,能不能找到一个通用的神经网络计算——如果不能百分百覆盖所有的应用,哪怕能覆盖掉一部分也很好。另外,在保证足够大算力的同时,需要考虑能量效率问题。例如,我们想为手机增加人工智能功能,但如果增加一点点这样的功能,会使手机电池寿命突然减半,那么就肯定不可取。th5ednc

th5ednc

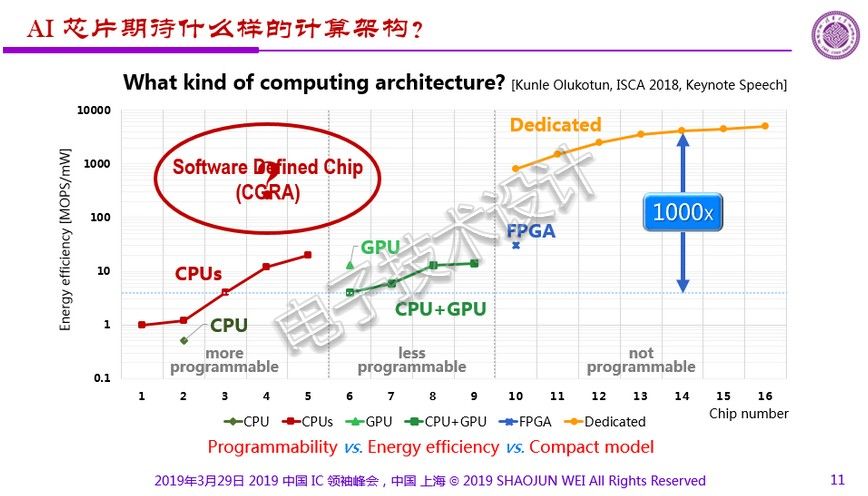

软件定义芯片是AI芯片的发展方向

魏教授认为AI芯片未来的发展方向是软件定义芯片。如下图所示,GPU相比CPU没有太大的变化,但是FPGA特别是ASIC时就会发生重大变化。th5ednc

th5ednc

对于未来芯片架构的创新,软件定义芯片,或者称粗粒度可重构架构(CGRA),这个概念比较热,即要去兼顾硬件可编程性与软件可编程性。这个概念在国际半导体技术路线图(ITRS)和美国国防高级研究计划局(DARPA)的ERI项目中都有规划。魏教授表示:“它应该是软件、硬件均可以编程,而且是混合颗粒度的。它虽然能量效率和计算效率比不上专用集成电路,但一定是比起CPU、GPU要好很多。”th5ednc

th5ednc

总结

魏教授感悟说,我们做芯片的人苦,为了实现差异化,不停地在定义、设计、制造、销售这个周期中打转。随着时间的推移,芯片的价值在降低,差异化在变小。但如果我们设计的芯片能像人类的成长过程一样,通过接受教育而变得跟别人不一样,那么我们的芯片将越用越有价值,越用差异化越大。这是实现竞争的一个非常重要的方法。th5ednc

如果能做到这一点,我们就可以通过不断地在使用过程当中获取相关的参数,获取学习的内容,进一步发展,最终形成芯片的个性化。随着时间的推移,个性化越来越强。“这样的发展思路也许对我们今后发展人工智能,甚至不仅仅是人工智能,在发展个性化、差异化的芯片过程当中,会起到很重要的作用。”魏教授总结说。th5ednc

上一篇

上一篇